## Digital Semiconductor SA-110 Microprocessor Evaluation Board

## **Reference Manual**

Order Number: EC-QU5KA-TE

The EBSA-110 is an evaluation board for the SA-110 StrongARM<sup>®</sup> microprocessor. This manual is the single point-of-reference for all users of the EBSA-110. It is a configuration guide, a programmers' guide and a technical reference.

**Revision/Update Information:** Version 1.0.

#### March 1996

While Digital believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

© Digital Equipment Corporation 1996. All rights reserved.

The following are trademarks of Digital Equipment Corporation: Digital, Digital Semiconductor and the DIGITAL Logo.

Digital Semiconductor is a Digital Equipment Corporation business.

ABEL is a registered trademark of Data I/O Corporation.

Altera is a registered trademark of Altera Corporation.

ARM and StrongARM are registered trademarks of ARM Ltd.

Intel is a registered trademark of Intel Corporation.

PostScript is a registered trademark of Adobe Systems Incorporated.

Quickswitch is a registered trademark of Quality Semiconductor, Inc.

TimingDesigner is a registered trademark of Chronolgy.

VIEWlogic is a registered trademark of Viewlogic Systems Inc.

Windows is a trademark of Microsoft Corporation.

All other trademarks and registered trademarks are the property of their respective holders.

This document was prepared using VAX DOCUMENT, Version 2.1.

## Contents

| Preface |                                                                                                                                                                          | xi                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Getting                                                                                                                                                                  | g Started                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                |

|         | 1.1<br>1.2<br>1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.3.1<br>1.4<br>1.5                                                                                                    | Physical Description         Handling Precautions         Visual Inspection         Cabling         Links         Socketed Components                                                                                                                                                                                                                                               | 1-1<br>1-1<br>1-3<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4                                                                                           |

| 2       | Functi                                                                                                                                                                   | onal Specification                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                |

|         | 2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.6.1<br>2.6.2<br>2.6.3<br>2.6.4<br>2.6.5<br>2.6.6<br>2.7<br>2.8<br>2.9<br>2.10 | CPU<br>Clocks<br>Reset<br>Power<br>Voltage Domains<br>Power Sequencing<br>Memory<br>ROM<br>SSRAM<br>DRAM<br>Memory Map Switching<br>I/O Sub-System<br>Serial Ports and Printer Port<br>Ethernet Port and UID ROM<br>PCMCIA Controller<br>Counter/Timer<br>Soft I/O<br>Architectural Compliance Verification Facilities<br>Interrupts<br>JTAG<br>Hardware Debug Support<br>Expansion | $\begin{array}{c} 2-1\\ 2-1\\ 2-3\\ 2-3\\ 2-3\\ 2-4\\ 2-4\\ 2-4\\ 2-4\\ 2-5\\ 2-5\\ 2-5\\ 2-5\\ 2-6\\ 2-6\\ 2-6\\ 2-6\\ 2-6\\ 2-6\\ 2-6\\ 2-6$ |

|         | 2.11<br>2.12<br>2.13<br>2.14                                                                                                                                             | Control Logic<br>Endian Issues<br>LEDs<br>On-Board Software                                                                                                                                                                                                                                                                                                                         | 2–7<br>2–7<br>2–8<br>2–8                                                                                                                       |

## 3 Programmers' Guide

| 3.1     | Memory Map                        | 3–1  |

|---------|-----------------------------------|------|

| 3.1.1   | Memory Map After Reset            | 3–3  |

| 3.1.2   | Characteristics of Memory         | 3–4  |

| 3.2     | Memory Map Decodes                | 3–4  |

| 3.2.1   | DRAM Space                        | 3–4  |

| 3.2.2   | DRAM Configuration Space          | 3–5  |

| 3.2.3   | Synchronous SRAM (SSRAM) Space    | 3–5  |

| 3.2.4   | EPROM/Flash Space                 | 3–5  |

| 3.2.5   | I/O Space                         | 3–6  |

| 3.2.6   | RW_ABORT Space                    | 3–7  |

| 3.2.7   | R_ABORT Space                     | 3–7  |

| 3.2.8   | ISAMEM Space                      | 3–7  |

| 3.2.8.1 | EBUFMEM Space                     | 3–8  |

| 3.2.8.2 | PCMCIAMEM Space                   | 3–8  |

| 3.2.9   | ISAIO Space                       | 3–8  |

| 3.3     | The PIT Registers                 | 3–9  |

| 3.4     | The SuperI/O Registers            | 3–10 |

| 3.5     | The Ethernet Controller Registers | 3–11 |

| 3.6     | The PCMCIA Controller Registers   | 3–12 |

| 3.7     | The Soft Register                 | 3–12 |

| 3.8     | Reset State                       | 3–13 |

| 3.9     | Software Restrictions             | 3–13 |

| 3.9.1   | 8-bit Accesses to Odd Addresses   | 3–13 |

## 4 Interrupts

| 4.1   | Distinguishing CTB_OS, CTB_ARCH Under Software Control | 4–2 |

|-------|--------------------------------------------------------|-----|

| 4.2   | CTB_OS                                                 | 4–2 |

| 4.2.1 | The FIQ_MASK Register                                  | 4–2 |

| 4.2.2 | The IRQ_MASK Register                                  | 4–3 |

| 4.2.3 | The IRQ_MSET, IRQ_MCLR Registers                       | 4–3 |

| 4.2.4 | The IRQ_RAW Register                                   | 4–4 |

| 4.2.5 | The IRQ_MSKD Register                                  | 4–4 |

| 4.3   | CTB_ARCH                                               | 4–4 |

| 4.3.1 | The FIQ_MASK Register                                  | 4–4 |

| 4.3.2 | The IRQ_MASK Register                                  | 4–5 |

| 4.3.3 | The IRQ_CNT Cycle Counter Register                     | 4–5 |

| 4.3.4 | The FIQ_CNT Cycle Counter Register                     | 4–6 |

## 5 Configuration of Memory and VLSI Devices

| 5.1   | Configuring Cacheable/Non-Cacheable Space | 5–1 |

|-------|-------------------------------------------|-----|

| 5.2   | Switching the Memory Map                  | 5–1 |

| 5.3   | DRAM                                      | 5–1 |

| 5.3.1 | Disable Refresh Requests                  | 5–2 |

| 5.3.2 | Initialize the DRAM                       | 5–2 |

| 5.3.3 | Enable Refresh Requests                   | 5–3 |

| 5.3.4 | Determine the DRAM Type                   | 5–3 |

| 5.3.5 | Size the Memory                           | 5–3 |

| 5.3.6 | Test the memory                           | 5–4 |

| 5.4   | SSRAM                                     | 5–4 |

| 5.5   | EPROM                                     | 5–4 |

| 5.6   | Flash                                     | 5–4 |

| 5.7   | PCMCIA Controller                             | 5–4 |

|-------|-----------------------------------------------|-----|

| 5.7.1 | Setting the PCMCIA Socket Programming Voltage | 5-5 |

| 5.7.2 | Setting a PCMCIA Socket Memory Window         | 5–5 |

| 5.8   | Ethernet Controller                           | 5–7 |

| 5.8.1 | Send the Initiation Key                       | 5–7 |

| 5.8.2 | Put the Device into 'CONFIG' State            | 5–7 |

| 5.8.3 | Configure the Plug-and-play Registers         | 5–8 |

| 5.8.4 | Disable the Plug-and-play Registers           | 5–8 |

| 5.9   | Super I/O Controller                          | 5–9 |

| 5.10  | Programmable Interval Timer                   | 5–9 |

#### 6 Performance

| 6.1   | Synchronous SRAM Accesses          | 6–1 |

|-------|------------------------------------|-----|

| 6.2   | EDO DRAM Accesses                  | 6–1 |

| 6.3   | BEDO DRAM Accesses                 | 6–2 |

| 6.4   | Performance Impact of DRAM Refresh | 6–3 |

| 6.5   | EPROM and Flash Accesses           | 6–3 |

| 6.6   | I/O Accesses                       | 6–4 |

| 6.6.1 | Ethernet Buffer Memory Bandwidth   | 6–4 |

| 6.7   | Overlap of Cycles                  | 6–4 |

## 7 Software Development Environment

| 7.1     | Loadable Debuggable Images | 7–1 |

|---------|----------------------------|-----|

| 7.1.1   | Building                   | 7–1 |

| 7.1.2   | Run Time Environment       | 7–2 |

| 7.1.2.1 | Memory Map                 | 7–2 |

| 7.1.2.2 | C Library Support          | 7–2 |

| 7.1.2.3 | Exception Vectors          | 7–2 |

| 7.1.2.4 | Access to I/O Devices      | 7–2 |

| 7.2     | Standalone Flash Images    | 7–2 |

| 7.2.1   | Building                   | 7–2 |

| 7.2.2   | Run Time Environment       | 7–3 |

| 7.2.2.1 | Memory Map                 | 7–3 |

| 7.2.2.2 | C Library Support          | 7–3 |

| 7.2.2.3 | Exception Vectors          | 7–3 |

| 7.2.2.4 | Access to I/O Devices      | 7–3 |

#### 8 On-Board Software

| 8.1   | The Primary Boot Loader              | 8–1 |

|-------|--------------------------------------|-----|

| 8.2   | The Format of Images in Flash        | 8–2 |

| 8.3   | The Startup EPROM                    | 8–3 |

| 8.4   | Diagnostics                          | 8–4 |

| 8.4.1 | Getting Ready to Run the Diagnostics | 8–4 |

| 8.4.2 | Description of Tests                 | 8–4 |

#### 9 Software Utilities

| 9.1   | The Flash Management Utility        | 9–1 |

|-------|-------------------------------------|-----|

| 9.1.1 | When to Specify the Block Number    | 9–3 |

| 9.1.2 | When to Specify the 'NoBoot' Option | 9–4 |

| 9.2   | The Bootp Utility                   | 9–4 |

| 9.2.1 | Variants of the bootp Program       | 9–5 |

## 10 Theory of Operation

| 10.1 A   | A Tour of the Schematics                              | 10–1  |

|----------|-------------------------------------------------------|-------|

| 10.1.1   | Principal Buses                                       | 10–2  |

| 10.1.2   | Power                                                 | 10–3  |

| 10.1.3   | Decoupling                                            | 10–3  |

| 10.1.4   | Voltage Levels                                        | 10–4  |

| 10.1.5   | Clocks                                                | 10–4  |

| 10.1.6   | Reset                                                 | 10–5  |

| 10.1.7   | The CPU                                               | 10–6  |

| 10.1.8   | Jumpers, Etch Links, Debug Connectors and Test Points | 10–6  |

| 10.1.9   | SSRAM Interface                                       | 10–7  |

| 10.1.10  | Buffering                                             | 10–7  |

| 10.1.11  | DRAM Interface                                        | 10–7  |

| 10.1.12  | Control Logic                                         | 10–8  |

| 10.1.13  | EPROM/Flash                                           | 10–8  |

| 10.1.14  | SuperI/O Controller                                   | 10–9  |

| 10.1.15  | Ethernet Controller                                   | 10–10 |

| 10.1.16  | PCMCIA Controller                                     | 10–11 |

| 10.1.17  | JTAG Port                                             | 10–11 |

| 10.1.18  | Counter/Timer                                         | 10–12 |

| 10.2 (   | Control Logic                                         | 10–12 |

| 10.2.1   | Control of CPU Bus Cycles                             | 10–14 |

| 10.2.2   | Types of Cycles                                       | 10–15 |

| 10.2.3   | Sub-Block Wrapping                                    | 10–15 |

| 10.2.4   | The Burst Counter                                     | 10–15 |

| 10.2.5   | The Packer Address Counter                            | 10–17 |

| 10.2.6   | Accesses to 16-bit Peripherals                        | 10–18 |

| 10.2.7   | Memory Map Switching After Reset                      | 10–18 |

| 10.2.8   | BEDO DRAM Configuration Cycles                        | 10–19 |

| 10.2.9   | Address Decoding                                      | 10–19 |

| 10.2.9.1 | Decoding Within the SSRAM Quadrant                    | 10–20 |

| 10.2.9.2 | Decoding Within the DRAM Quadrant                     | 10–20 |

| 10.2.9.3 | Decoding Within the ROM Quadrant                      | 10–20 |

| 10.2.9.4 | Decoding Within the IO Quadrant                       | 10–21 |

| 10.3     | Timing Analysis                                       | 10–21 |

|          | Expanding the EBSA-110                                | 10–21 |

|          | The Printed Circuit Board                             | 10–22 |

| 10.6 I   | Design Improvements                                   | 10–22 |

#### 11 Simulation Waveforms

| 11.1  | automap   | 11–1  |

|-------|-----------|-------|

| 11.2  | ss_wcrd   | 11–3  |

| 11.3  | ss_wcwr   | 11–3  |

| 11.4  | ss_rdwrap | 11–6  |

| 11.5  | ss_rdall  | 11–8  |

| 11.6  | ed_wcrd   | 11–10 |

| 11.7  | ed_wcwr   | 11–12 |

| 11.8  | ed_rdwrap | 11–14 |

| 11.9  | bd_wcrd   | 11–14 |

| 11.10 | bd_wcwr   | 11–17 |

| 11.11 | bd_rdwrap | 11–19 |

| 11.12 | bd_wrf    | 11–21 |

| 11.13 | rfrsh     | 11–21 |

| 11.14 | cbr       | 11–24 |

| 11.15 | romrd1    | 11–26 |

| 11.16 | romrd2    | 11–28 |

| 11.17 | flashwr   | 11–30 |

| 11.18 | io        | 11–30 |

| 11.19 | iordy     | 11–34 |

| 11.20 | iozws     | 11–34 |

| 11.21 | iorfrdy   | 11–34 |

| 11.22 | iotrick   | 11–38 |

## A Configuration Guide

| A.1     | Default Configuration            | A–1  |

|---------|----------------------------------|------|

| A.2     | Description of All Jumpers       | A–1  |

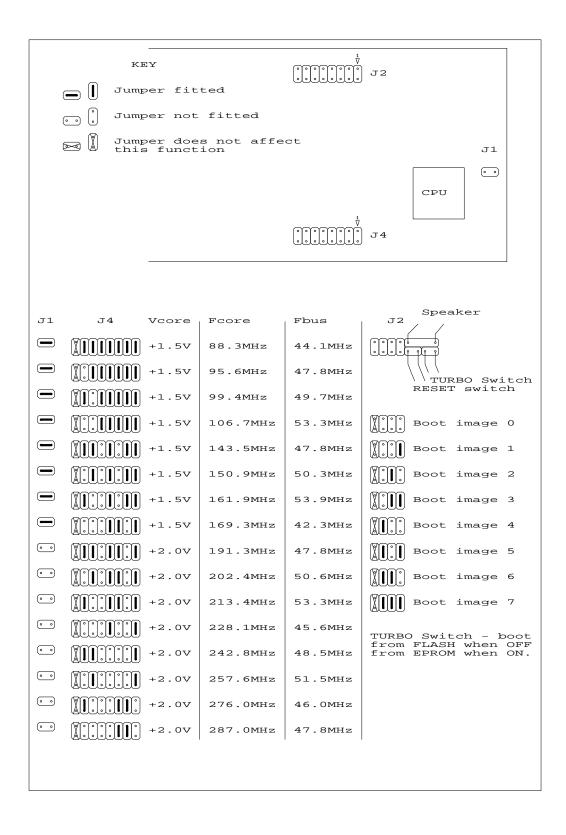

| A.2.1   | Supported Clock Configurations   | A–5  |

| A.3     | Description of All Links         | A–5  |

| A.4     | Connectors                       | A–6  |

| A.5     | Debug Connectors                 | A–7  |

| A.6     | Debug Pick-up Points             | A–8  |

| A.7     | LEDs                             | A–8  |

| A.8     | Cables Within the Enclosure      | A–9  |

| A.8.1   | Power Supply                     | A–9  |

| A.8.2   | Serial Ports                     | A–10 |

| A.8.3   | Parallel Port                    | A–10 |

| A.8.4   | Reset Switch                     | A–10 |

| A.8.5   | Turbo Switch                     | A–10 |

| A.8.6   | Loudspeaker                      | A–10 |

| A.9     | Cables for External Connection   | A–10 |

| A.9.1   | Serial Ports                     | A–10 |

| A.9.1.1 | Serial Cable for SUN Workstation | A–11 |

| A.9.2   | Parallel Port                    | A–11 |

| A.9.3   | Parallel Port Loopback           | A–12 |

| A.9.4   | Ethernet Port                    | A–12 |

| A.9.5   | JTAG Port                        | A–12 |

| A.10    | Upgrading the DRAM SIMMs         | A–13 |

#### B Debugging a Broken Board

| B.1 | Basic Checks       | B–1 |

|-----|--------------------|-----|

| B.2 | Checking the Board | B–1 |

| B.3 | Diagnostic Failure | B–2 |

#### C The Design Database

#### D SA-110 Bus Transactor Model User's Guide

| D.1   | Instantiating the Model                            | D–2 |

|-------|----------------------------------------------------|-----|

| D.2   | Command Reference                                  | D–3 |

| D.2.1 | set_addr {address}                                 | D–3 |

| D.2.2 | set_page {offset}                                  | D–3 |

| D.2.3 | <pre>set_bytes {byte masks}, set_size {size}</pre> | D–3 |

| D.2.4 | do_rd {expected read data}                         | D–4 |

| D.2.5 | do_crd {expected read data}                        | D–4 |

| D.2.6 | do_wr {write data}                                 | D–4 |

| D.2.7 | do_fwr {write data}                                | D–4 |

| D.2.8 | do_idle {number of cycles}                         | D–4 |

| D.2.9 | do_swap {expected read data} {write data}          | D–4 |

| D.3   | How It Works                                       | D–4 |

| D.4   | It Is Not Idiot-Proof!                             | D–5 |

| D.4.1 | Completeness, Known Bugs and Model Support         | D–6 |

| D.4.2 | Porting, Modifying and Rebuilding                  | D–6 |

|       |                                                    |     |

#### E ABEL Tutorial

#### F Getting Started with an Uncased Board

| F.0.1 | Choosing a Power Supply | F–1 |

|-------|-------------------------|-----|

|       | Choosing an Enclosure   | F–1 |

#### **G** Technical Support and Ordering Information

#### Index

#### Figures

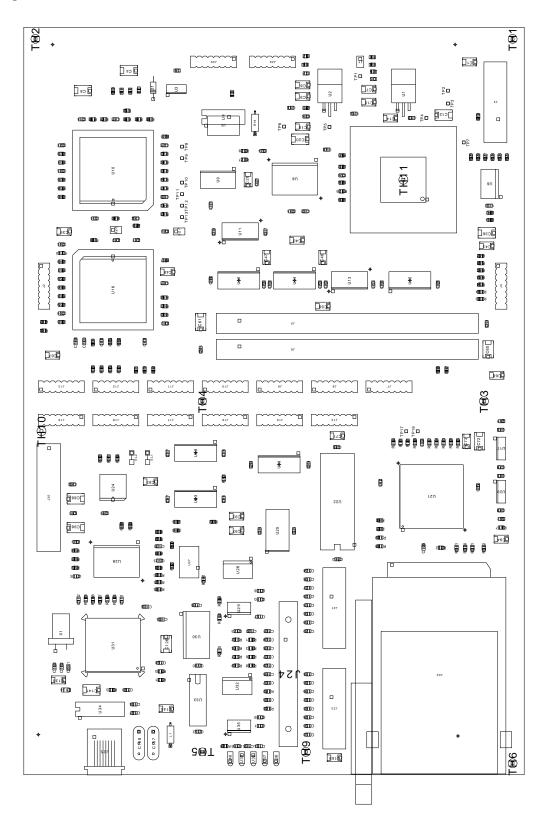

| 1–1  | The EBSA-110 Board     | 1–2   |

|------|------------------------|-------|

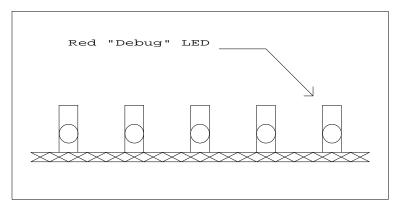

| 1–2  | Position of Debug LED  | 1–4   |

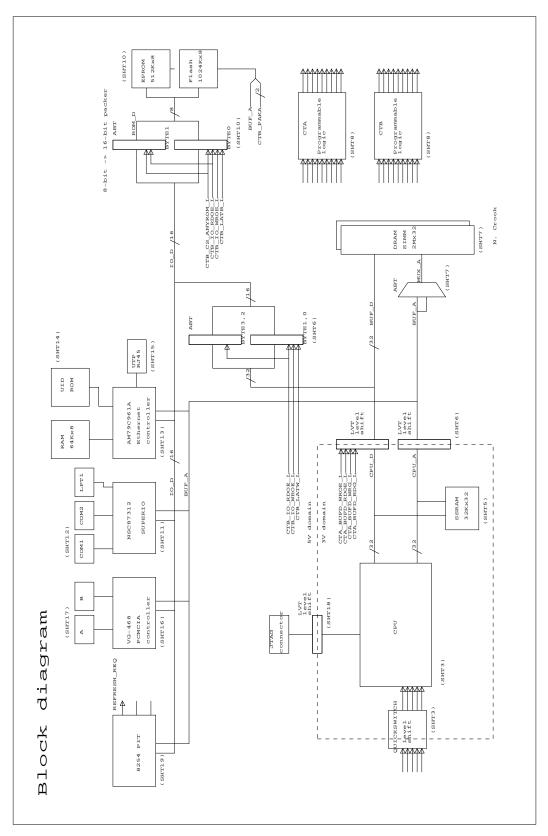

| 2–1  | EBSA-110 Block Diagram | 2–2   |

| 11–1 | automap                | 11–2  |

| 11–2 | ss_wcrd                | 11–4  |

| 11–3 | ss_wcwr                | 11–5  |

| 11–4 | ss_rdwrap              | 11–7  |

| 11–5 | ss_rdall               | 11–9  |

| 11–6 | ed_wcrd                | 11–11 |

| 11–7 | ed_wcwr                | 11–13 |

| 11–8 | ed_rdwrap              | 11–15 |

| 11–9  | bd_wcrd                      | 11–16 |

|-------|------------------------------|-------|

| 11–10 | bd_wcwr                      | 11–18 |

| 11–11 | bd_rdwrap                    | 11–20 |

| 11–12 | bd_wrf                       | 11–22 |

| 11–13 | rfrsh                        | 11–23 |

| 11–14 | cbr                          | 11–25 |

| 11–15 | romrd1                       | 11–27 |

| 11–16 | romrd2                       | 11–29 |

| 11–17 | flashwr                      | 11–31 |

| 11–18 | io                           | 11–32 |

| 11–19 | iordy                        | 11–35 |

| 11–20 | iozws                        | 11–36 |

| 11–21 | iorfrdy                      | 11–37 |

| 11–22 | iotrick                      | 11–39 |

| A–1   | EBSA-110 Configuration Links | A–2   |

| A–2   | Position of LEDs             | A–9   |

#### Tables

| 3–1  | Memory Map                                             | 3–1   |

|------|--------------------------------------------------------|-------|

| 3–2  | Addresses in External-Decode Space                     | 3–9   |

| 3–3  | PIT Internal Registers                                 | 3–10  |

| 3–4  | SuperI/O Registers                                     | 3–10  |

| 3–5  | Ethernet Controller Registers                          | 3–11  |

| 3–6  | Bit Assignment of Soft Register                        | 3–12  |

| 4–1  | Interrupt Control Registers - CTB_OS Configuration     | 4–1   |

| 4–2  | Interrupt Control Registers - CTB_ARCH Configuration   | 4–1   |

| 4–3  | FIQ Mask Bit Positions                                 | 4–2   |

| 4–4  | Interrupt Mask Bit Positions - CTB_OS Configuration    | 4–3   |

| 4–5  | FIQ Mask Bit Positions                                 | 4–4   |

| 4–6  | Interrupt Mask Bit Positions - CTB_ARCH Configuration  | 4–5   |

| 5–1  | PCMCIA Controller Configuration Sequence               | 5–4   |

| 5–2  | PCMCIA Programming Voltages                            | 5–5   |

| 5–3  | Ethernet Plug-and-play Register Configuration Sequence | 5–8   |

| 5–4  | Ethernet Plug-and-play Register Initial Values         | 5–8   |

| 6–1  | Stalls Added During EDO DRAM Accesses                  | 6–2   |

| 6–2  | Stalls Added During BEDO DRAM Accesses                 | 6–2   |

| 6–3  | Stalls Added During EPROM and Flash Accesses           | 6–4   |

| 6–4  | Stalls Added During I/O Accesses                       | 6–4   |

| 6–5  | Stalls Caused by Back-to-Back Cycles                   | 6–5   |

| 8–1  | Boot Image Selection                                   | 8–1   |

| 8–2  | Flash Image Header                                     | 8–3   |

| 8–3  | Selecting Diagnostics                                  | 8–4   |

| 10–1 | Byte/Half-Word Decode Using SA0, SBHE_L                | 10–18 |

| A–1  | Jumpers                                                | A–3   |

| A–2  | Links                                                  | A–5   |

| A–3  | Connectors                                             | A–6   |

| A–4  | Debug Connectors                 | A-7  |

|------|----------------------------------|------|

| A–5  | Pick-up point                    | A–8  |

| A–6  | Null-MoDem Cable                 | A–10 |

| A–7  | SUN Null-MoDem Cable             | A–11 |

| A–8  | Bidirectional Parallel Cable     | A–11 |

| A–9  | Parallel Port Loopback Connector | A–12 |

| A–10 | JTAG Cable                       | A–12 |

| A–11 | Suitable DRAM SIMMs              | A–13 |

## Preface

#### Introduction

The EBSA-110 is an evaluation board for Digital Semiconductor's SA-110 microprocessor. It is designed to meet the following requirements:

- To provide a power-on vehicle for the SA-110 chip.

- To provide an environment in which to run the ARM® architectural compliance software test suite.

- To provide a non-proprietary example design.

- To provide a software development environment, including a fast memory sub-system on which to run software benchmarks.

This document is a single point-of-reference both for configuring and using the board and for engineers wishing to copy parts of its design. As such, it has the following scope:

- Functional specification

- Theory of operation (to be read in conjunction with the circuit schematics)

- · Configuration guide (memory options, speed options, jumper and link options)

- Programmers' guide (memory maps, boot process, references to programmble I/O devices on the board)

This document does not aim to duplicate material to be found elsewhere. Specifically, it does not duplicate material that is to be found in vendor data sheets for components used in the design, nor does it document the ARM software development environment.

#### How to Use This Document

All readers should turn to Chapter 1 for information about how to connect and power-on the board, how to verify that it is working correctly and how to connect it to a terminal or host system.

All readers are advised to read Chapter 2 to get an understanding of the overall functionality of the board. Subsequent chapters assume a familiarity with the material in this chapter.

Thereafter, software engineers will probably want to refer to the following chapters:

- Chapter 3 is a guide to the memory map of the board and the address decoding of all I/O devices.

- Chapter 4 describes the interrupt structures.

- Chapter 5 is a guide to configuration of the memory and VLSI devices on the board.

- Chapter 7 is a brief introduction to the software development environment.

- Chapter 8 describes the on-board software, including the power-on sequence of the board, and the power-on diagnostics.

- Chapter 9 describes software utilities which are provided with the EBSA-110.

- Chapter 6 contains performance-related information, and documents the cycle times required for accessing various devices on the board.

Hardware engineers will probably want to refer to the following chapters:

- Chapter 10 is a detailed technical description of the hardware of the board, including a theory of operation.

- Chapter 11 describes a number of simulation waveforms, giving a deeper insight into the operation of the EBSA-110 control state machines.

A number of appendices provide general reference material:

- Appendix A describes all of the link and jumper options present on the board, and all of the cables that may be required for connection to the board.

- Appendix B provides hints on how to track down faults on the EBSA-110.

- Appendix C describes the machine-readable design databases for the EBSA-110 hardware and software.

- Appendix D describes the operation and usage of the SA-110 Bus Transaction Model, which is provided as part of the design database.

- Appendix E is a brief tutorial in the ABEL® PLD synthesis language used to describe the state machines in the EBSA-110 design.

- Appendix F describes how to choose a suitable enclosure and power supply for the board.

- Appendix G describes other relevant documents and services that are available from Digital and its partners.

#### Notation

All numbers are shown in decimal unless otherwise stated.

All hexadecimal numbers have an 0x prefix. 32-bit hex values have dots for ease of reading. Examples are: 0xfe0b.3004, 0xfb.

All binary number have an 0b prefix; long numbers include dots for ease of reading. Examples are: 0b00, 0b0000.0000.1010.0000.

This document refers to an 8-bit data unit as a byte, a 16-bit data unit as a half-word and a 32-bit data unit as a longword.  $\dagger$

This document uses the notation INTn to refer to a naturally-aligned block of n bytes. Thus, an INT4 is an aligned 32-bit value whilst an INT32 is eight 32-bit values on a naturally aligned address (this corresponds to the size and alignment of an SA-110 cache block).

<sup>&</sup>lt;sup>†</sup> Standard ARM notation is to use the terms byte, half-word and word, respectively. Digital's convention is to use the terms byte, word and longword. Therefore, this document avoids use of the term 'word', which is ambiguous to different audiences.

Electrical signal names are shown thus: **cpu\_wait\_l**. An **\_l** at the end of a signal name indicates that the signal is asserted (active) when it is low (close to 0V).

#### References

This section provides a selective bibliography and a reference to relevant manufacturers' data sheets. ARM-specific and SA-110-specific information is referenced in Appendix G.

- 1. SSRAM: Micron MT58LC32K36C4-LG (or MT58LC32K36D7-LG) data sheet.

- PCMCIA controller: VADEM VG-468 PC Card Socket Controller Data Manual (December 1993, Rev 02, or later). VADEM, San Jose, CA. Tel +1 408 943-9301. Fax +1 408 943-9735. UK distributor: MMD. Tel +44 1734 633700.

- 3. Super I/O: PC87312 data sheet, National Semiconductor Corporation.

- 4. EDO DRAM: Micron MT16D232M-6 X DRAM Module data sheet.

- 5. Burst EDO DRAM: Micron MT4D232M-6 ES DRAM Module data sheet.

- 6. Flash ROM: 28F008SA data sheet, Intel order number 290429-004.

- 7. EPLD: EPM7096LC84-7, Altera 1995 Data Book.

- 8. Ethernet controller: Advanced Micro Devices Am79C961A data sheet (AMD publication number 19364 Rev. A (October 1994) with Amendment sheet 1)

- 9. High-Speed Digital Design a handbook of black magic. (Howard W Johnson, Martin Graham, 1993 Prentice Hall ISBN 0-13-395724-1).

# Getting Started

The EBSA-110 is provided built, tested and cased. This chapter provides a physical description of the board and then describes how to:

- 1. Perform a visual inspection of the EBSA-110.

- 2. Power-on the EBSA-110 for the first time.

- 3. Attach the EBSA-110 to a terminal or host system.

If you wish to use a different enclosure for the board, refer to Appendix F for details on choosing a suitable power supply and enclosure.

#### 1.1 Physical Description

The EBSA-110 is shown in Figure 1–1. It is a single-board computer designed to match the form-factor of a baby-AT PC motherboard. This allows it to be mounted in a standard desktop or deskside PC cabinet. Flying leads connect the board to its I/O connectors. The I/O connectors are mounted in break-out holes that are standard on these systems. The board is powered from the cabinet's power supply using the standard PC power connectors.

#### 1.2 Handling Precautions

The EBSA-110 contains components that are susceptible to permanent damage from electrostatic discharge ('static' electricity). Risk of damage can be alleviated by following a few simple handling precautions.

If the EBSA-110 was supplied cased and you remove the cover, ensure that the case is earthed and that you are wearing an antistatic wrist strap before making any adjustments to the board.

If the EBSA-110 is supplied as a bare board, it is supplied in an antistatic bag. Do not remove the board from the bag unless you are working on an antistatic earthed surface and wearing an antistatic wrist strap. Always adopt these precautions when handling the board.

#### **1.3 Visual Inspection**

When you receive your unit, you should perform these minimum checks:

- Inspect the enclosure for physical damage.

- Check the power supply line input voltage is correct for your geography.

Even if your EBSA-110 was provided as a cased unit, you may still want to take the lid off and perform the following checks:

• Internal cables fully attached

#### Getting Started 1.3 Visual Inspection

Figure 1–1 The EBSA-110 Board

- Links attached and correctly set

- Socketed components properly seated

More details are provided below for this second set of checks.

#### 1.3.1 Cabling

Identify each of the cables and ensure that it is correctly polarized and fully mated to the appropriate connector on the board:

- Power connectors: There are two 6-way power connectors. The 4 black cables align with the connector pins marked 'GND' on the board.

- Reset cable: This 2-way cable can be connected either way around. The board connector is marked 'RESET'.

- COM1 cable: This is a ribbon cable with pin 1 marked by a colored stripe. The board connector is marked 'COM1' and pin 1 is marked by a '1' and a pointer.

- COM2 cable: This is identical to the COM1 cable. The board connector is marked 'COM2' and pin 1 is marked by a '1' and a pointer.

- LPT cable: This is a ribbon cable with pin 1 marked by a colored stripe. The board connector is marked 'LPT1' and pin 1 is marked by a '1' and a pointer.

Refer to Appendix A if you cannot identify the connectors.

#### 1.3.2 Links

Verify that all jumpers are pushed fully down on their mounting posts.

If any jumpers have come off or you are unsure about their positions, refer to Section A.1 for a description of the default settings.

#### **1.3.3 Socketed Components**

Verify that any socketed devices (the programmable devices, the DRAM SIMMs and the EPROM (if fitted)) are fully mated in their sockets.

#### 1.3.3.1 The CPU

The EBSA-110 is designed so that the CPU can be soldered directly to the board, or fitted in a socket. Some boards have the CPU fitted in a socket. Do not tamper with the socket or remove the CPU unless you have a good reason to. The CPU is removed by pressing down on the socket frame that surrounds the CPU, then lifting the CPU out using a vacuum pencil. In the absence of a vacuum pencil, you can use something sticky on the blunt end of a pencil. Take care not to bend any CPU leg during this process, as it may result in an intermittent electrical contact when you replace the CPU.

Note \_\_\_\_\_

The CPU socket is not polarized. When viewing the EBSA-110 so that the CPU is in the bottom right-hand corner of the board, the CPU is correctly orientated when its pin 1 (marked by a circle) is in the bottom left-hand corner of the chip.

#### 1.4 Power-On

The initial test of the board should be performed with no cables attached to the system, apart from the power cable. Make a note of the jumpers fitted (if any) to J2 pins 9-10, 11-12, 13-14, 15-16. Remove any jumpers from these pins. This will force the board to execute its start-up software and then enter the ARM remote debug stub.

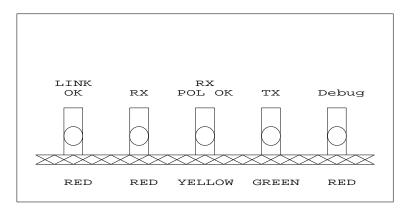

There are a group of 5 LEDs on the rear of the unit. Use Figure 1-2 to identify the 'debug' LED. Watch this LED as you power-on the board. The LED should be off whilst the board is reset, then on for about 0.5s whilst the ARM remote debug stub initializes, then turn off and remain off.

Now attach a terminal or terminal emulator to the COM1 port on the EBSA-110. The terminal should be configured for 9600 baud, 8-bit data, 1 stop bit, no parity, no flow control. After you reset or power-cycle the system, you should see a message like this on the terminal:

ARMa100, DEMON V1.1, 0x40020000 bytes RAM, ROM CRC OK, Little endian

If the system fails to behave as described, or you wish to perform more thorough testing of the system, run the system diagnostics using the procedure described in Section 8.4. If the system behaves correctly, read on.

Figure 1–2 Position of Debug LED

#### 1.5 Attaching the EBSA-110 to a Terminal or Host System

When the EBSA-110 is used as a software development system, it is directly connected to a host system. The host system may be either a PC or a workstation. In either case, connection can be made in one of the following ways:

• Using a serial port

In this configuration, a cable connects the COM1 port on the EBSA-110 to the host system. The debug environment uses the serial link as a bidirectional link for commands and responses, and to download images from the host to the EBSA-110.

• Using the Ethernet †

<sup>&</sup>lt;sup>†</sup> The Ethernet option is not supported in the initial release of the software.

In this configuration, the EBSA-110 and the host system are both connected to an Ethernet LAN. The debug environment uses the LAN as a bidirectional link for commands and responses and to download images from the host to the EBSA-110.

Refer to Chapter 7 for more information on the software development environment.

When the EBSA-110 is running its power-on diagnostics, status and progress information are written to the COM1 port. The COM1 port should be connected to a terminal or terminal emulator configured for 9600 baud, 8-bit data, 1 stop bit, no parity, no flow control.

Refer to Chapter 8 for more information on the diagnostics.

If the EBSA-110 is used for some standalone application, that application may control all interfaces on the board. Refer to Section 7.2 for information on building standalone applications.

Refer to Section A.9 for details of the cables required in all these configurations.

## **2** Functional Specification

This chapter describes each functional element of the EBSA-110. More detailed information describing how the board works and how to program it can be found in later chapters of this document. Figure 2–1 is a block diagram of the board.

#### 2.1 CPU

The EBSA-110 uses the SA-110 microprocessor. The board allows the CPU to be operated at any of its 16 core clock frequencies (between 88.3 MHz and 287.0 MHz with the upper limit determined by the speed grade of the CPU that is fitted) and either of its two core voltages (+1.5V or +2.0V). You can set the core voltage and frequency using jumpers on the board.

The EBSA-110 uses the SA-110 pin-bus in the following modes:

- Synchronous bus mode (SA-110 generates the bus clock)

- Enhanced bus mode (cache wrapping and write buffer merging)

- Fastbus mode (delayed address timing)

For special applications, these modes can be changed by rewiring etch links on the board. Refer to Section A.3.

The CPU is packaged in a 144-pin thin quad flat-pack (TQFP). The EBSA-110 provides a dual-footprint layout to allow the CPU to be surface-mounted or to be fitted in a socket.

#### 2.2 Clocks

The EBSA-110 uses the following oscillators:

- 3.6864 MHz (baud-rate) oscillator for the SA-110. The oscillator is a standard surface-mounted (SMT) part with a TTL output and it relies on an external level converter to generate the +3.3V switching levels that are required by the CPU. The CPU uses an internal phase-locked loop (PLL) to generate its core clock from this clock.

- 24.0 MHz oscillator for the SuperI/O controller. This is an SMT part with a TTL output.

- 20.0 MHz crystal for the Ethernet controller. This is a 2-pin through-hole part. The Ethernet controller contains the circuitry to bias this crystal into oscillation.

## Functional Specification 2.2 Clocks

The SA-110 generates complementary output clocks **mclk**, **nmclk** by dividing down its core clock. The EBSA-110 is designed to run with a maximum **mclk** frequency of 55 MHz, and this corresponds to core clock divisors of between 2 and 5. **nmclk** is used to clock the on-board state machines and control logic.

Control logic on the board uses **nmclk** to generate a divided-by-seven clock (approximately 6 MHz) which is used in the I/O sub-system to clock the programmable interval timer and the PCMCIA controller.

All clocks have a low fanout, so no external clock buffering is used.

#### 2.3 Reset

A power-on reset is generated from an RC network and schmitt trigger arrangement. A 2-pole 0.1" pitch connector is provided to allow an external normally-open reset switch to be attached. In a lab environment, you can generate reset by shorting these poles with a screwdriver or jumper.

#### 2.4 Power

The EBSA-110 has the following power requirements:

- +5V +/- 5%, @ 1 Amp for the main logic

- +12V +/- 5%, @ 0.5 Amp for the Flash and PCMCIA sockets

The board will function without the +12V supply, with the restrictions that it will not be possible to program the Flash memory, and that there will be no +12V power available for plug-in PCMCIA cards  $\dagger$ . If your power supply does not supply +12V, the +12V supply rail should be left disconnected.

Several devices on the board require +3.3V and this is generated from +5V using an adjustable linear regulator.

The CPU core requires +1.5V or +2.0V (depending upon the core clock frequency). This is generated from +3.3V using an adjustable linear regulator. You can select the regulator output using a jumper.

#### 2.4.1 Voltage Domains

The SA-110 outputs use +3.3V switching levels, and the inputs are not +5V-tolerant (they cannot withstand +5V TTL switching levels). The synchronous SRAM's outputs use +3.3V switching levels, but the inputs *are* +5V-tolerant. All the remaining devices on the board are +5V-tolerant.

The following interfacing techniques are used on the board:

- 74LVT devices are used as voltage converters. These parts have a +3.3V supply and are +5V-tolerant. Their output switching range is within the TTL switching threshold and so they can drive TTL-level devices powered from +5V. 74LVT devices are used as interfaces on the CPU address and data buses.

- Output signals from +3.3V devices can be used to drive TTL-level inputs directly. This method is used to interface SA-110 outputs to the system control logic.

<sup>&</sup>lt;sup>†</sup> This is most likely to affect PCMCIA disk drives and Flash cards.

• Quality Semiconductor 'QuickSwitch®' devices are used as voltage converters. These devices perform voltage conversion with 'zero' (actually, around 250ps) delay. These parts are used to interface clocks and system control logic outputs to SA-110 inputs.

#### 2.4.2 Power Sequencing

The SA-110 requires two voltage supplies; a +3.3V supply to powers its primary input/output buffers (the pin bus) and a +1.5V or +2.0V supply to power its core. The +3.3V supply must become stable earlier than the core voltage supply. This requirement prevents any possibility of latch-up within parasitic structures on the SA-110. This requirement is satisfied on the EBSA-110 by deriving the +2.0V supply from the +3.3V supply, rather than directly from the +5.0V supply.

There are no other power-sequencing requirements.

#### 2.5 Memory

The EBSA-110 provides three distinct memory regions:

- ROM: non-volatile storage for programs

- SSRAM: fast memory for time-critical code and data

- DRAM: for large code and data sets

#### 2.5.1 ROM

Non-volatile storage for the bootstrap program is provided in an EPROM (512Kbyte) or a Flash ROM (1024Kbyte). Both are 8-bit devices. They are mapped into different regions of the memory map. A user-configurable jumper determines which of them is decoded at address 0 (and therefore supplies the reset vector to the CPU after reset). Normally, the Flash ROM would be used, and the EPROM (which is socketed) would not be fitted. The EPROM is provided for manufacturing use and as insurance against the user unwittingly deleting the primary bootstrap image from the Flash.

CPU reads from the ROM are automatically packed to provide INT4s to the CPU. This is achieved by a state sequence that reads four consecutive bytes from the ROM in response to the CPU access. This packing is transparent to the CPU, and does not affect the format or ordering of data programmed into the ROM.

During CPU writes, consecutive locations in the Flash are sparsely addressed. The mapping is described in Section 3.2.4.

CPU reads from the ROM can be sequential or non-sequential cycles.

CPU writes to the Flash (to program it) must be non-sequential cycles.

#### 2.5.2 SSRAM

A region of fast RAM is implemented using a single 32Kx32 synchronous static RAM (SSRAM) device. This provides 128Kbytes. Alternatively, the circuit-board footprint for the SSRAM can accommodate the 64Kx36 device, when it becomes available. This memory region should be used for speed-critical code and data, when possible.

#### 2.5.3 DRAM

Two 72-pin 5V DRAM memory SIMMs can be fitted. The DRAM memory controller supports Extended Data Out (EDO) and Burst EDO (BEDO) parts with an access time of 60ns or better. The first generation of BEDO parts are available as 2Mx32 SIMMs, so two SIMMs provide a total of 16Mbytes of DRAM.

The memory controller uses the ID signals from a DRAM SIMM to automatically accommodate SIMMs of various sizes.

The memory controller is soft-configurable between EDO and BEDO operation, and the bootstrap software automatically determines the memory type during the power-on sequence.

If two SIMMs are fitted, they must be of the same size and type.

The DRAMs are periodically refreshed using a CAS-before-RAS sequence. The refresh sequence is initiated by a timer which is initialized by the bootstrap software during the power-on sequence.

The DRAM controller is simple-minded in two ways:

- It will always satisfy the RAS precharge time between a pair of accesses, even if the accesses are to separate physical banks of DRAM.

- It does not interleave (neither between banks in a SIMM nor between SIMMs)

Sequential cycles from the CPU are always performed as page-mode DRAM accesses and conversely, the DRAM controller will always terminate a page mode cycle when the CPU terminates its sequential access (it does not speculatively keep the page open).

#### 2.5.4 Memory Map Switching

Immediately after reset, the CPU fetches its reset vector from address 0. During normal operation, it is preferable to have RAM at address 0. The EBSA-110 control logic allows the memory map to be switched to accommodate these requirements. The process is described in Section 3.1.1.

#### 2.6 I/O Sub-System

All I/O on the EBSA-110 is performed as programmed I/O under the control of the CPU. The I/O sub-system provides the following resources:

- 2 RS232 serial ports with PC-style 9-way D-connectors

- 1 bidirectional PC-style parallel printer port with 25-way D-connector

- Ethernet port with 10BaseT (twisted pair) media support on an RJ45 jack connector

- Ethernet Unique ID ROM

- PCMCIA controller

- 3-channel counter/timer

- Soft-programmable outputs

- Soft-readable inputs

- Architectural compliance verification facilities

#### 2.6.1 Serial Ports and Printer Port

The serial and parallel ports are implemented using a National Semiconductor PC87312 SuperI/O III chip. This part also includes a floppy disk controller and decodes for an IDE interface but these functions are not used in this design.

#### 2.6.2 Ethernet Port and UID ROM

The Ethernet port is implemented using a National Semiconductor Am79C961A 'ISA-net' controller operated in shared-memory mode. The UID ROM is accessed via the AM79C960. In shared-memory mode, the Am79C961A uses external RAM as temporary data storage. This external RAM is attached to the Am79C961A and is accessible to the CPU via the Am79C961A.

The Ethernet port only supports the 10BaseT (UTP) media. 10BaseT requires a hub-based topology but can also be used point-to-point between two nodes.

#### 2.6.3 PCMCIA Controller

Two PCMCIA sockets are supported, using a Vadem VG468 controller. Socket A is the socket closer to the board. Both socket A and socket B can support Type I, II and III PCMCIA cards. A Type III card in Socket A will mechanically obscure Socket B, preventing it from being used.

#### 2.6.4 Counter/Timer

The counter/timer is implemented using an Intel® 82C54 Programmable Interval Timer (PIT). The PIT is a three-channel device. One channel is dedicated to producing a periodic signal for the memory controller in order to initiate DRAM refresh. The other two channels are available for application software; their timeout outputs can be used to generate interrupts to the CPU.

#### 2.6.5 Soft I/O

The soft I/O is implemented within programmble logic. There are 4 read/write outputs (the written value can be read back by the CPU) and 4 read-only inputs. These signals are used to control various on-board functions, including an LED. The bits are described in Section 3.7.

#### 2.6.6 Architectural Compliance Verification Facilities

The programmable control logic implements some facilities which are used for architectural verification. This functionality duplicates facilities that exist in the silicon development environment for the SA-110. These facilities are:

- The ability to generate ABORTs to the CPU on certain read and write cycles.

- The ability to generate interrupts as the result of a timeout on a programmable down-counter that has been loaded by the CPU and then decremented at the rate of the system bus clock.

These facilities are described in more detail in Section 3.2.6, Section 3.2.7 and Chapter 4.

These facilities are not required during normal operation and the resources that they use within the programmble logic are reassigned to provide an interrupt controller.

#### 2.7 Interrupts

The EBSA-110 includes a simple interrupt controller that can be used to support re-entrant interrupts and lowest-latency 'priority levels' on the flat interrupt structure that the single IRQ interrupt provides. The interrupt controller is described in Chapter 4.

#### 2.8 JTAG

A 7x2 header is fitted to provide electrical access to the EBSA-110 JTAG port. The SA-110 only provides boundary scan access.

#### 2.9 Hardware Debug Support

The EBSA-110 provides connectors and test points to make it easy to attach a logic analyzer to the board. The pickups are of two types:

- The buffered address and data buses and some other low-speed signals are routed to 16-pin 2x8 header plugs. These are suitable for direct connection to a Tektronix DAS logic state analyzer and can be connected to any other analyzer using 'grabber' probes.

- Various control signals have etch vias on their routing to allow a Harwin post to be soldered into the board. This allows a logic analyzer to be attached, but does not interfere with the high-speed signals by adding additional etch length and capacitance.

As always, the additional load imposed by test equipment may interfere with the normal operation of the board.

#### 2.10 Expansion

The EBSA-110 has no standard expansion capability. However, the control signals present on the debug connectors are sufficient to allow I/O devices to be interfaced via a mezzanine PCB. This is discussed in Section 10.4.

#### 2.11 Control Logic

All of the control logic for the CPU, memory and I/O sub-systems is implemented within two 84-pin PLCC programmable logic parts. The source files for these parts are provided as part of the design database, allowing you to modify them if required.

The control logic is described in detail in Section 10.2.

#### 2.12 Endian Issues

The SA-110 can be configured as a little-endian or a big-endian machine †. The

<sup>&</sup>lt;sup>†</sup> The terms 'little-endian' and 'big-endian' have been adopted by the computer industry to describe the way in which bytes are ordered within larger data units. Machines which treat the byte on the low-order data bus lines (the byte with the lowest address) as the least-significant byte are termed 'little-endian'. Machines which use the opposite ordering (most-significant byte at the lowest address) are termed 'big-endian'. The VAX is a little-endian machine, as is the Intel x86 family. The Motorola 68xx family is big-endian. Most modern RISC implementations are ambi-endian; they can be configured to run with either endian-ness. The term 'endian' comes from Jonathan Swift's "Gulliver's Travels". The two great empires of Lilliput and Blefuscu were engaged in a most obstinate war as the result of an edict published by the Emperor of Lilliput. In this edict, the Emperor did command "all his subjects, upon great penalties, to break the smaller end of their eggs". Many hundred large volumes have been published upon this controversy: but the books of the Big-Endians have been long forbidden. Swift's

recommended mode of operation is little-endian, and this is the default state after reset. The EBSA-110 can be operated with either endian-ness, with no impact on the hardware. The on-board software is configured for little-endian operation. If big-endian operation is required, the following changes must be made:

- The definitions of all I/O addresses must be changed. For example, a bytewide I/O device at address 0 on a little-endian machine will be at address 3 on a big-endian machine.

- The byte ordering within the ROM must be changed; the ROM packer hardware (refer to Section 2.5.1) packs bytes from the ROM into a little-endian order, so a big-endian image must be pre-scrambled to compensate (the alternative is to redesign the packer sequencer in the control logic).

#### 2.13 LEDs

The EBSA-110 has 4 LEDs, which are used to provide information on the status of the Ethernet link, and a further 1 LED that is used to provide debug information. Section A.7 describes the LEDs.

#### 2.14 On-Board Software

The EBSA-110 on-board software is programmed into the Flash ROM. The Flash can contain a number of independent images. At a minimum, the Flash contains a program called the Primary Bootstrap Loader (PBL). The PBL can load and start a specified image stored in Flash. By default, it starts up the ARM remote debugger stub. A power-on diagnostic suite is also programmed into the Flash and can be selected by changing jumpers on the board.

invention was a satire on the Spanish war of succession and a commentary on the history of religious controversy in England. The analogy to computer byte ordering is poor. Whilst it is true "That all true believers shall break their eggs at the convenient end", (in other words, endian-ness in egg consumption is irrelevant) the relative endian-ness of a pair of computers can be important when they want to exchange data.

## **3** Programmers' Guide

This chapter is a reference for programmers. It describes the memory map of the board, the reset state of the system and software programming restrictions.

#### 3.1 Memory Map

The SA-110 has a 32-bit address bus with byte addressability and a 32-bit data bus. The address space is divided into quadrants based on A[31:30] and devices have multiple aliases in each quadrant.

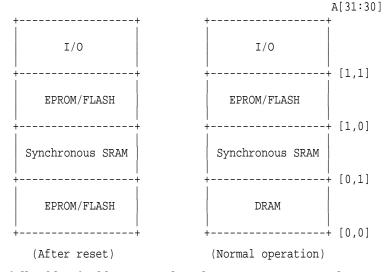

An overview of the memory map is shown below:

A full table of addresses within the memory space is shown in Table 3–1. Section 3.2 describes how the memory space is decoded.

Table 3–1 Memory Map

| Address     | Name      | Function                     |

|-------------|-----------|------------------------------|

| 0xffff.ffff | ISAIO_END | Last location in ISAIO space |

| 0xf3c0.0000 | TRICK7    | Interrupt control            |

| 0xf380.0000 | TRICK6    | Interrupt control            |

| 0xf340.0000 | TRICK5    | Interrupt control            |

| 0xf300.0000 | TRICK4    | Interrupt control            |

| 0xf2c0.0000 | TRICK3    | Interrupt control            |

|             |           | (continued on next next      |

(continued on next page)

| Address     | Name           | Function                                                          |

|-------------|----------------|-------------------------------------------------------------------|

| 0xf280.0000 | TRICK2         | Interrupt control                                                 |

| 0xf240.0000 | TRICK1         | Soft registers                                                    |

| 0xf200.000d | PIT_CTLW       | Control Word register                                             |

| 0xf200.0009 | PIT_CNT2       | Counter 2 register                                                |

| 0xf200.0005 | PIT_CNT1       | Counter 1 register                                                |

| 0xf200.0001 | PIT_CNT0       | Counter 0 register                                                |

| 0xf200.0000 | TRICK0         | PIT registers base                                                |

| 0xf200.0000 | ISAIO_EDBASE   | Start of external-decode ISAIO space                              |

| 0xf000.0000 | (free)         | This area is free for other ISAIO stuff                           |

| 0xf000.14f1 | PNP_WRDATA     | Plug-and-play Auto-Configuration write-<br>data port (write-only) |

| 0xf000.0ffc | SIO_COM1END    | Last SuperI/O COM1 register                                       |

| 0xf000.0fe0 | SIO_COM1BASE   | Start of SuperI/O COM1 registers                                  |

| 0xf000.0e64 | SIO_DATA       | SuperI/O (configuration) data register                            |

| 0xf000.0e60 | SIO_INDEX      | SuperI/O (configuration) index register                           |

| 0xf000.0dfc | SIO_LPT2END    | Last SuperI/O LPT2 register                                       |

| 0xf000.0de0 | SIO_LPT2BASE   | Start of SuperI/O LPT2 registers                                  |

| 0xf000.0bfc | SIO_COM2END    | Last SuperI/O COM2 register                                       |

| 0xf000.0be0 | SIO_COM2BASE   | Start of SuperI/O COM1 registers                                  |

| 0xf000.07c1 | PCMCIA_DATA    | PCMCIA controller Data register                                   |

| 0xf000.07c0 | PCMCIA_INDEX   | PCMCIA controller Index register                                  |

| 0xf000.04f1 | PNP_ADDRESS    | Plug-and-play Auto-Configuration address port (write-only)        |

| 0xf000.046c | NET_IDP        | ISACSR register data port                                         |

| 0xf000.0468 | NET_RESET      | Reset the controller                                              |

| 0xf000.0464 | NET_RAP        | Register address port (shared by RDP and IDP)                     |

| 0xf000.0460 | NET_RDP        | Register data port                                                |

| 0xf000.0440 | NET_UID        | Ethernet UID address PROM (16 bytes)                              |

| 0xf000.0405 | PNP_RDDATA     | Plug-and-play Auto-Configuration read-<br>data port (read-only)   |

| 0xf000.0000 | ISAIO_SDBASE   | Start of self-decode ISAIO space                                  |

| 0xf000.0000 | ISAIO_BASE     | Start of ISAIO space                                              |

| 0xefff.ffff | ISAMEM_END     | Last location in ISAMEM space                                     |

| 0xea00.0000 | (free)         | This area is free for other ISAMEM allocation                     |

| 0xe9ff.ffff | PCMCIAMEM_END  | Last location in PCMCIA reserved space                            |

| 0xe800.0000 | PCMCIAMEM_BASE | Start of PCMCIA reserved space                                    |

| 0xe7ff.ffff | EBUFMEM_ALIASE | End of last Ethernet buffer memory alias                          |

|             |                | (continued on next page)                                          |

Table 3–1 (Cont.) Memory Map

#### Programmers' Guide 3.1 Memory Map

| Address     | Name          | Function                                |

|-------------|---------------|-----------------------------------------|

| 0xe001.ffff | EBUFMEM_END   | Last location of Ethernet buffer memory |

| 0xe000.0000 | EBUFMEM_BASE  | Start of Ethernet buffer memory         |

| 0xe000.0000 | ISAMEM_BASE   | Start of ISAMEM space                   |

| 0xdfff.ffff | RW_ABORT_END  | Last location in Read/Write-Abort space |

| 0xd000.0000 | RW_ABORT_BASE | Start of Read/Write-Abort space         |

| 0xcfff.ffff | R_ABORT_END   | Last location in Read-Abort space       |

| 0xc000.0000 | R_ABORT_BASE  | Start of Read-Abort space               |

| 0x8fff.ffff | ROM_ALIASE    | End of last ROM alias                   |

| 0xa007.ffff | EPROM_END     | Last location in EPROM memory           |

| 0xa000.0000 | EPROM_BASE    | Start in EPROM memory                   |

| 0x800f.ffff | FLASH_END     | Last location in Flash memory           |

| 0x8000.0000 | FLASH_BASE    | Start of Flash memory                   |

| 0x7fff.ffff | SSRAM_ALIASE  | End of last SSRAM alias                 |

| 0x4002.0000 | SSRAM_ALIASS  | Start of first SSRAM alias              |

| 0x4001.ffff | SSRAM_END     | Last location of SSRAM memory           |

| 0x4000.0000 | SSRAM_BASE    | Start of SSRAM memory                   |

| 0x3fff.ffff | DRAM_ALIASE   | End of last DRAM alias                  |

| 0x00ff.ffff | DRAM_16M      | End of first 16Mbytes of DRAM           |

| 0x00bf.ffff | DRAM_12M      | End of first 12Mbytes of DRAM           |

| 0x007f.ffff | DRAM_8M       | End of first 8Mbytes of DRAM            |

| 0x003f.ffff | DRAM_4M       | End of first 4Mbytes of DRAM            |

| 0x0000.0000 | DRAM_BASE     | Start of DRAM memory                    |

Table 3–1 (Cont.) Memory Map

#### 3.1.1 Memory Map After Reset

After reset, the SA-110 fetches its reset vector from address 0. Therefore, it is necessary to have ROM at this address immediately after reset. This is achieved by decoding the EPROM/Flash in two quadrants immediately after reset. The memory map is switched under software control. The first write performed by the SA-110 (after reset) will switch the memory map to normal operation. The memory map switch occurs *after* the write cycle completes. Therefore, if the write is to address 0, the data will not be written to the DRAM, but will be written to EPROM/Flash space (that is, the write will be ignored † ). If two writes to address 0 are performed, the second will successfully write data to the DRAM.

Due to the very low performance of ROM accesses (each 32-bit access is performed by packing data from 4 successive locations in the 8-bit ROM) the image to be executed should normally be copied into RAM first. Before starting a copy, the software should jump to the high-order alias of the ROM and switch the address map.

It is not possible to reverse this address map switching process under software control.

<sup>&</sup>lt;sup>†</sup> The Flash ROM is sensitive to writes; that is how it is given commands and programmed. However, each of the commands requires a pair of bus cycles with specific (different) data so this switching mechanism is safe.

#### 3.1.2 Characteristics of Memory

The SSRAM is small and fast (factor of 1), the DRAM is large and quite fast (factor of 1/2 - 1/3), the EPROM/Flash is very slow (factor of 1/16).

Because of the slow speed of the EPROM/Flash access, is is best to copy images from EPROM/Flash into SSRAM or DRAM and execute them from there.

#### 3.2 Memory Map Decodes

This section describes how the memory space is decoded. It provides essentially the same information as Table 3–1, but in a greater level of detail.

The diagrams in the following sections use this key:

```

0 - must be 0

```

```

1 - must be 1

```

- A significant to address a location within device

- a significant to address optional locations within device (eg alternative memory size)

- X don't-care: significant to address aliases within device

- - not available (A1, A0 represent byte lanes on the 32-bit bus)

#### 3.2.1 DRAM Space

$1 \ 0 \ 9 \ 8 \ 7 \ 6 \ 5 \ 4 \ 3 \ 2 \ 1 \ 0 \ 9 \ 8 \ 7 \ 6 \ 5 \ 4 \ 3 \ 2 \ 1 \ 0$

This decodes the DRAM. Zero, one or two DRAM SIMMs may be fitted. They must be 72-pin +5V types, either x32 or x36. The hardware automatically detects and accommodates 1Mx32, 2Mx32 and 4Mx32 SIMMs. This means that the board can accommodate up to 32Mbytes of DRAM. The DRAM controller can support EDO and BEDO parts. If two SIMMs are fitted, they must be the same size and type. The memory is contiguous and byte addressable. There are multiple aliases of the DRAM in the system address space. The hardware reads all bytes of a longword during reads, and performs byte masks during writes.

The DRAM is not accessible immediately after reset (see Section 3.1.1).

#### 3.2.2 DRAM Configuration Space

When BEDO DRAMs are fitted, a special pair of cycles, CBR (CAS-before-RAS) and WCBR (write CAS-before-RAS), must be performed in order to configure the DRAMs. EDO DRAMs require no configuration.

These cycles are performed by setting the DCBR (do CAS-before-RAS) bit in the Soft register and then performing read and write cycles to the normal DRAM space.

When performing these configuration cycles, the data written is irrelevant; the value on the low-order address lines configures the DRAMs. The following addresses should be used:

The effect of this write is to set the BEDO DRAM burst ordering to 'linear'. After performing the write (or all writes) a read should be performed to the same address. This restores the DRAM to normal operation. After all CBR and WCBR cycles have been completed, the DCBR bit should be cleared.

The configuration process is described in detail in Section 5.3.

#### 3.2.3 Synchronous SRAM (SSRAM) Space

This decodes the synchronous SRAM (SSRAM). There are multiple aliases. The SSRAM is contiguous and byte addressable. The hardware reads all bytes of a longword during reads, and performs byte masks during writes. The SSRAM is either 128Kbyte or 256Kbyte. 128Kbyte is the normal size.

#### 3.2.4 EPROM/Flash Space

This decodes the EPROM/Flash. In normal operation, S=0 decodes the Flash, and S=1 decodes the EPROM. Therefore, the Flash will be decoded at address 0 after reset and so the system will boot from Flash. If the jumper EPROM\_BOOT is fitted, the behavior of S is inverted, and so the system will boot from EPROM. Usually, there is no need to fit the EPROM. The EPROM socket and EPROM\_BOOT facility are provided for manufacturing and as an 'emergency repair' mechanism in case the Flash is programmed with a bad image.

The EPROM is a 512Kbyte device, and is read-only. The Flash is a 1Mbyte device and is readable and sector writeable. Refer to the manufacturer's data sheet for programming details.

Since the EPROM and the Flash are byte-wide devices, they are accessed via a packer mechanism which assembles a 32-bit data unit from an aligned address. This is transparent to the software during reads, but affects the way in which byte accesses are performed when writing to the Flash.

When writing to the Flash, the data must always be supplied on the low-order byte lane. This corresponds to byte writes to addresses 0, 4, 8 and so on. The actual byte addressability is provided by the address lines marked 'b' above. Therefore, the first 9 byte locations in Flash are addressed as:

0x0000.0000 0x0040.0000 0x0080.0000 0x00c0.0000 0x0000.0004 0x0040.0004 0x0080.0004 0x00c0.0004 0x00c0.0004

Writes to the Flash are always performed as non-sequential cycles, so the Flash must not be placed in cacheable space during programming and the write buffer must not be used for writes to the Flash.

#### 3.2.5 I/O Space

All devices in the I/O space quadrant are 8-bit or 16-bit devices and are physically attached to one or both of the two low-order byte lanes of the data bus. Since the data bus is actually 32-bits wide, addresses in I/O space are not contiguous.

Byte masks are only partially decoded in this space and so writes to incorrect addresses are more likely to corrupt a device than to be ignored.

In a little-endian system, all valid byte addresses in this space end in 0b00 or 0b01, and all valid half-word addresses end in 0b00.

The I/O space quadrant is further subdivided into quadrants:

- ISAIO space

- ISAMEM space

- RW\_ABORT space

- R\_ABORT space

#### 3.2.6 RW\_ABORT Space

The RW\_ABORT space is an architectural compliance verification facility; it is unlikely to be useful in normal applications.

Any reads or writes within this address range will result in an abort exception. Sequential cycles to this address space will result in an abort exception for each data beat of the sequential cycle.

#### 3.2.7 R\_ABORT Space

The R\_ABORT space is an architectural compliance verification facility; it is unlikely to be useful in normal applications.

Any reads within this space will result in an abort exception. Writes will be ignored. Sequential writes to this address space will be ignored. Sequential reads to this address space will result in an abort exception for each data beat of the sequential cycle.

#### 3.2.8 ISAMEM Space

The ISAMEM space is used to access devices which behave like ISA-bus memory devices. This includes PCMCIA card resources (accessed through the PCMCIA controller) and the Ethernet controller's buffer memory.

The address ranges occupied by PCMCIA card resources and the Ethernet controller are software configurable.

Cycles in ISAMEM space are controlled using memr\_l, memw\_l, zws\_l and rdy.

| A  | I | A | А | А | А | А | А | А | А | А | А | А | А | А | А | А | А | А | А | А | А | А |   |   |   |   |   |   |   |   |   |   |             |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------------|

| 3  | 3 | 3 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | А | А | А | А | А | А | А | А | А | Α |             |

| 1  | 0 | ) | 9 | 8 | 7 | б | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | б | 5 | 4 | 3 | 2 | 1 | 0 |             |

| +- |   |   |   | + | + |   |   | + | + |   |   |   | + |   |   |   | + |   |   |   | + |   |   | + | + |   |   | + | + |   | + | + | -           |

|    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | - | IO quadrant |

|    | 1 | L | 1 | 0 | Х | Х | Х | Х | Х | Х | Х | Х | X | Х | Х | Х | Х | Х | Х | Х | X | Х | Х | Х | Х | Х | Х | Х | Х | Х | - | - | ISAMEM      |

#### 3.2.8.1 EBUFMEM Space

The Ethernet controller maintains transmit and receive data structures in a piece of shared memory. This memory is decoded within the ISAMEM space in the address range where **a**[27]=0, that is:

The EBUFMEM is accessed using byte and half-word read/writes. It appears in the address space as 16-bit memory and so its locations are non-contiguous.

The algorithm to convert an offset *a* in EBUFMEM space into an address is:

address = (a & 1) | ((a & 0xffff.fffe) << 1) | 0xe000.0000

#### 3.2.8.2 PCMCIAMEM Space

Resources on PCMCIA cards are accessed by configuring the PCMCIA controller to open windows in the ISAMEM space. The addresses must be selected to fall into an address range where a[27]=1<sup>†</sup>, that is:

Refer to Section 5.7.2 for a worked example of setting a PCMCIA window.

The PCMCIAMEM is accessed using byte and half-word read/writes. It appears in the address space as 16-bit memory and so its locations are non-contiguous.

The algorithm to convert an offset *a* in PCMCIAMEM space into an address is:

address = (a & 1) | ((a & 0xffff.fffe) << 1) | 0xe000.0000

#### 3.2.9 ISAIO Space

The ISAIO space is used to access devices which behave like ISA-bus I/O devices. This includes the PIT, the Soft I/O register, the interrupt control registers, the SuperI/O registers, the PCMCIA internal control registers, PCMCIA card resources (accessed through the PCMCIA controller) and some of the Ethernet controller registers.

The address ranges occupied by PCMCIA card resources and the Ethernet controller are software configurable.

<sup>†</sup> There is no hardware checking of this restriction, because the PCMCIA controller cannot decode a[27]. If you try to map memory into the area of ISAMEM space where a[27]=0, you will cause bus contention with the EBUFMEM area.

Cycles in ISAIO space are controlled using ior\_l, iow\_l, zws\_l and rdy.

The ISAIO space is divided into two regions:

- The first region is for ISA-like devices that decode their own addresses based on the expectation that the whole I/O space is limited to a 10-bit decode (I/O addresses 0-0x3FF). a[25]=0 is used to select these devices.

- The second region is for devices that require external address decode logic.

The following devices sit in self-decoding space:

- SuperI/O controller

- Ethernet controller

- PCMCIA controller (including resources on PCMCIA cards)

The following devices sit in external-decode space:

- PIT

- Soft register

- Interrupt control registers

These devices are further decoded using **a**[**24**:**22**]. The addresses of these registers are shown in Table 3–2. For more information on the PIT, soft register and interrupt control registers, refer to Section 3.3, Section 3.7 and Chapter 4.

| Address     | Name   | Function          |  |

|-------------|--------|-------------------|--|

| 0xf3c0.0000 | TRICK7 | Interrupt control |  |

| 0xf380.0000 | TRICK6 | Interrupt control |  |

| 0xf340.0000 | TRICK5 | Interrupt control |  |

| 0xf300.0000 | TRICK4 | Interrupt control |  |

| 0xf2c0.0000 | TRICK3 | Interrupt control |  |

| 0xf280.0000 | TRICK2 | Interrupt control |  |

| 0xf240.0000 | TRICK1 | Soft registers    |  |

| 0xf200.0000 | TRICK0 | PIT registers     |  |

Table 3–2 Addresses in External-Decode Space

# 3.3 The PIT Registers

The Programmable Interval Timer (PIT) is an Intel 82C54. It is physically attached to bits 15:8 of the data bus.

The PIT has three timer channels. All are clocked by **ctb\_clkby7**, which has a nominal frequency of 7.6 MHz. Channel 0 is used to provide a refresh request for the DRAM; its configuration is described in Section 5.3. Channels 1 and 2 are uncommitted, and may be used to generate interrupts to the CPU.

The PIT is decoded in external-decode ISAIO space. It has 4 memory-mapped registers which are accessed by byte read/writes to the addresses shown in Table 3–3.

| Address     | Name                  |  |

|-------------|-----------------------|--|

|             |                       |  |

| 0xf200.000d | Control Word register |  |

| 0xf200.0009 | Counter 2 register    |  |

| 0xf200.0005 | Counter 1 register    |  |

| 0xf200.0001 | Counter 0 register    |  |

Table 3–3 PIT Internal Registers

# 3.4 The SuperI/O Registers

The SuperI/O controller is a National Semiconductor PC87312. It is physically attached to bits 7:0 of the data bus.

The SuperI/O controller has 4 groups of registers which are decoded in selfdecoding ISAIO space. It is accessed using byte read/writes to the addesses shown in Table 3–4.

Table 3–4 SuperI/O Registers

| Port Address | ISAIO Address | Name  | Function                             |

|--------------|---------------|-------|--------------------------------------|

| 0x03f8       | 0xf000.0fe0   | COM1  | COM1 UART base address               |

| 0x02f8       | 0xf000.0be0   | COM2  | COM2 UART base address               |

| 0x0378       | 0xf000.0de0   | LPT2  | LPT2 printer port base address       |

| 0x0398       | 0xf000.0e60   | INDEX | Configuration index register address |

| 0x0399       | 0xf000.0e64   | DATA  | Configuration data register address  |

The positions of these registers are software configurable, but you are recommended to leave them at their power-on defaults.

For the SuperI/O controller, use this algorithm to convert an I/O address, *a*, into an ISAIO address:

ISAIO\_address = (a << 2) | 0xf000.0000

'take the port address, left shift by 2 bits then OR with 0xf000.0000'</pre>

For programming information, refer to the manufacturer's data sheet.

# 3.5 The Ethernet Controller Registers

The Ethernet controller is an AMD Am79C961A. It is physically attached to bits 15:0 of the data bus.

The Ethernet controller is decoded in self-decoding ISAIO space. It has 2 groups of registers which are accessed by byte and half-word read/writes:

- 3 Auto-Configuration registers. These registers are used to access indirectly the Plug-and-play (PNP) configuration registers.

- Access registers. These registers are used to access directly the Unique ID (UID) PROM and to access indirectly the internal resources of the Ethernet controller.

The register addresses are shown in Table 3–5.

| Port Address | ISAIO Address | Name        | Function                                                             |

|--------------|---------------|-------------|----------------------------------------------------------------------|

| 0x0279       | 0xf000.04f1   | PNP_ADDRESS | Plug-and-play Auto-<br>Configuration address port<br>(write-only)    |

| 0x0a79       | 0xf000.14f1   | PNP_WRDATA  | Plug-and-play Auto-<br>Configuration write-data port<br>(write-only) |

| 0x0203       | 0xf000.0405   | PNP_RDDATA  | Plug-and-play Auto-<br>Configuration read-data port<br>(read-only)   |

| 0x0220       | 0xf000.0440   | NET_UID     | Ethernet UID address PROM<br>(16 bytes)                              |

| 0x0230       | 0xf000.0460   | NET_RDP     | Register data port                                                   |